**User's Manual**

|                                                                                        |                            | ADSP-21010                              |       |

|----------------------------------------------------------------------------------------|----------------------------|-----------------------------------------|-------|

| 8E+005-0.8740E+081-3.1201E+225+8.1854E+22<br>-054-6.8774E+123+5.1297E+184+8.1530E+091+ |                            | ADSP-21020                              |       |

| -7.0626E-305+4.8715E+110+0.4322E+028+4.025                                             |                            |                                         | ••    |

| 17+7.0042E+026+8.3738E-184-1.7055E+296+7.                                              |                            | • • • • • • • • • • • • • • • • • • • • | •••   |

| E+002-6.9510E-253-7.1667E+124+7.5179E+166                                              | 3-3.2090E-247-3.5186       |                                         |       |

| 598E-256-5.7625E+054-6.8774E+123+5.1297E-                                              | +184+8.1530E+091+7.8       | • • • • • • • • • • • • • • • • • • • • | ••    |

| 1.2728E+279-7.0428E+005-0.8740E+081-3.120                                              |                            |                                         |       |

| +210-5.0591E+182-7.0626E-305+4.8715E+110+1                                             | 0.4322E+028+4.0257E-       |                                         |       |

| 0E+208-24652E+201+71042E +VC0+0.2720E =1                                               | 84 - 1.7055E + 296 + 7.381 |                                         |       |

|                                                                                        |                            |                                         |       |

|                                                                                        | 297E+269+6.5789E+23        | • • • • • • • • • • • • • • • • • • • • | ••    |

|                                                                                        | -6.9510E-253-7.1667E       |                                         |       |

| THO TOL TTO TO TO TOLEL                                                                | 8E+279-7.0428E+005         |                                         | ••    |

|                                                                                        | 8F+279-7 0428F+005         |                                         |       |

| E-098-7.7360E+243-                                                                     | B-2.4652E+201+7.0042       |                                         |       |

| 186E+017-1.5297E+20                                                                    |                            | •••••••                                 | •••   |

|                                                                                        | 79E+166-3.2090E-247        |                                         |       |

|                                                                                        | 5.1297E+184+8.1530E        |                                         |       |

| 7E-276-1.2728E+279-7.0428E+005-0.8740E+0                                               |                            |                                         |       |

| .3810E+210-5.0591E+182-7.0626E-305+4.8715E                                             |                            |                                         |       |

| 6+5.8640E+208-2.4652E+201+7.0042E+026+8.3                                              | 738E-184-1.7055E+29        | • • • • • • • • • • • • • • • • • • • • | •••   |

| +234+2.5138E-184+5.7886E+011+2.6112E-098-                                              |                            |                                         |       |

| 667E+124+7.5179E+166-3.2090E-247-3.5186E+                                              | 017-1.5297E+269+6.5        |                                         | • • • |

| -6.8774E+123+5.1297E+184+8.1530E+091+7.877                                             |                            |                                         |       |

| -005-0.8740E+081-3.1201E+225+8.1854E+225+                                              |                            |                                         |       |

| 6E-305+4.8715E+110+0.4322E+028+4.0257E-27                                              | 76-12728E+279-7.042        |                                         |       |

ANALOG DEVICES

ADSP-21020 ADSP-21010

# **User's Manual**

You may contact the Digital Signal Processing Group in the following ways.

- By contacting your local Analog Devices Sales Representative

- For Marketing information, call (617) 461-3881 in Norwood, Massachusetts, USA

- For Applications Engineering information, call (617) 461-3672 in Norwood, Massachusetts, USA

- The Norwood office Fax number is (617) 461-3010

- The Norwood office may also be reached by

- Telex: 924491 TWX: 710/394-6577 Cables: ANALOG NORWOODMASS

- The DSP Group runs a Bulletin Board Service that can be reached at 300, 1200, 2400 or 9600 baud, no parity, 8 bits data, 1 stop bit by dialing:

(617) 461-4258

• By writing to:

Analog Devices DSP One Technology Way P.O. Box 9106 Norwood, MA 02062-9106 USA

### ADSP-21020/21010 User's Manual

© 1993 Analog Devices, Inc. ALL RIGHTS RESERVED

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use; nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under the patent rights of Analog Devices.

PRINTED IN U.S.A.

SECOND EDITION

- COMPUTATION UNITS 2

- PROGRAM SEQUENCING 3

- DATA ADDRESSING 4

- TIMER 5

7

8

9

A

B

C

D

- MEMORY INTERFACE 6

- **INSTRUCTION SUMMARY**

- ASSEMBLY PROGRAMMING TUTORIAL

- HARDWARE SYSTEM DESIGN

- INSTRUCTION SET REFERENCE

- COMPUTE OPERATION REFERENCE

- IEEE 1149.1 JTAG TEST ACCESS PORT

- NUMERIC FORMATS

- CONTROL/STATUS REGISTERS

## Contents **D**

#### CHAPTER 1 INTRODUCTION

| 1.1.2       Why Floating-Point?       1–3         1.1.3       Future Product Migration Path       1–4         1.2       ARCHITECTURE OVERVIEW       1–4         1.2.1       Computation Units       1–4         1.2.2       Address Generators And Program Sequencer       1–6         1.2.3       Interrupts       1–7         1.2.4       Timer       1–7         1.2.5       Memory Buses And Interface       1–7         1.2.6       Internal Data Transfers       1–8         1.2.7       Context Switching       1–8         1.2.8       Instruction Set       1–8         1.3       DEVELOPMENT SYSTEM       1–9 | 1.1   | GENERAL DESCRIPTION                      |       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------------------------------|-------|

| 1.1.2       Why Floating-Point?       1–3         1.1.3       Future Product Migration Path       1–4         1.2       ARCHITECTURE OVERVIEW       1–4         1.2.1       Computation Units       1–4         1.2.2       Address Generators And Program Sequencer       1–6         1.2.3       Interrupts       1–7         1.2.4       Timer       1–7         1.2.5       Memory Buses And Interface       1–7         1.2.6       Internal Data Transfers       1–8         1.2.7       Context Switching       1–8         1.2.8       Instruction Set       1–8         1.3       DEVELOPMENT SYSTEM       1–9 | 1.1.1 | Key Enhancements                         | <br>2 |

| 1.1.3       Future Product Migration Path       1–4         1.2       ARCHITECTURE OVERVIEW       1–4         1.2.1       Computation Units       1–4         1.2.2       Address Generators And Program Sequencer       1–6         1.2.3       Interrupts       1–7         1.2.4       Timer       1–7         1.2.5       Memory Buses And Interface       1–7         1.2.6       Internal Data Transfers       1–8         1.2.7       Context Switching       1–8         1.2.8       Instruction Set       1–8         1.3       DEVELOPMENT SYSTEM       1–9                                                   | 1.1.2 | Why Floating-Point?                      | <br>3 |

| 1.2       ARCHITECTURE OVERVIEW       1–4         1.2.1       Computation Units       1–4         1.2.2       Address Generators And Program Sequencer       1–6         1.2.3       Interrupts       1–7         1.2.4       Timer       1–7         1.2.5       Memory Buses And Interface       1–7         1.2.6       Internal Data Transfers       1–8         1.2.7       Context Switching       1–8         1.2.8       Instruction Set       1–8         1.3       DEVELOPMENT SYSTEM       1–9                                                                                                               | 1.1.3 | Future Product Migration Path            | <br>4 |

| 1.2.2         Address Generators And Program Sequencer         1–6           1.2.3         Interrupts         1–7           1.2.4         Timer         1–7           1.2.5         Memory Buses And Interface         1–7           1.2.6         Internal Data Transfers         1–8           1.2.7         Context Switching         1–8           1.2.8         Instruction Set         1–8           1.3         DEVELOPMENT SYSTEM         1–9                                                                                                                                                                   | 1.2   | ARCHITECTURE OVERVIEW                    | <br>4 |

| 1.2.2         Address Generators And Program Sequencer         1–6           1.2.3         Interrupts         1–7           1.2.4         Timer         1–7           1.2.5         Memory Buses And Interface         1–7           1.2.6         Internal Data Transfers         1–8           1.2.7         Context Switching         1–8           1.2.8         Instruction Set         1–8           1.3         DEVELOPMENT SYSTEM         1–9                                                                                                                                                                   | 1.2.1 | Computation Units                        | <br>4 |

| 1.2.3         Interrupts         1–7           1.2.4         Timer         1–7           1.2.5         Memory Buses And Interface         1–7           1.2.6         Internal Data Transfers         1–8           1.2.7         Context Switching         1–8           1.2.8         Instruction Set         1–8           1.3         DEVELOPMENT SYSTEM         1–9                                                                                                                                                                                                                                                | 1.2.2 | Address Generators And Program Sequencer | <br>6 |

| 1.2.4         Timer         1–7           1.2.5         Memory Buses And Interface         1–7           1.2.6         Internal Data Transfers         1–8           1.2.7         Context Switching         1–8           1.2.8         Instruction Set         1–8           1.3         DEVELOPMENT SYSTEM         1–9                                                                                                                                                                                                                                                                                               | 1.2.3 | Interrupts                               | <br>7 |

| 1.2.6         Internal Data Transfers         1–8           1.2.7         Context Switching         1–8           1.2.8         Instruction Set         1–8           1.3         DEVELOPMENT SYSTEM         1–9                                                                                                                                                                                                                                                                                                                                                                                                        | 1.2.4 | Timer                                    | <br>7 |

| 1.2.6         Internal Data Transfers         1–8           1.2.7         Context Switching         1–8           1.2.8         Instruction Set         1–8           1.3         DEVELOPMENT SYSTEM         1–9                                                                                                                                                                                                                                                                                                                                                                                                        | 1.2.5 | Memory Buses And Interface               | <br>7 |

| 1.2.8         Instruction Set         1–8           1.3         DEVELOPMENT SYSTEM         1–9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1.2.6 | Internal Data Transfers                  | <br>8 |

| 1.2.8         Instruction Set         1–8           1.3         DEVELOPMENT SYSTEM         1–9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1.2.7 | Context Switching                        | <br>8 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1.2.8 | Instruction Set                          | <br>8 |

| 1.4 MANUAL ORGANIZATION1-11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1.3   | DEVELOPMENT SYSTEM                       | <br>9 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1.4   | MANUAL ORGANIZATION                      | <br>1 |

### CHAPTER 2 COMPUTATION UNITS

| OVERVIEW                                            | 2–1                                                                                                                                                                                                                                                                                                                 |

|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IEEE FLOATING-POINT OPERATIONS                      | 2–2                                                                                                                                                                                                                                                                                                                 |

| Extended Floating-Point Precision (ADSP-21020 Only) | 2–3                                                                                                                                                                                                                                                                                                                 |

| Floating-Point Exceptions                           |                                                                                                                                                                                                                                                                                                                     |

| FIXED-POINT OPERATIONS                              | 2–4                                                                                                                                                                                                                                                                                                                 |

| ROUNDING                                            | 2–4                                                                                                                                                                                                                                                                                                                 |

| ALU                                                 | 2–5                                                                                                                                                                                                                                                                                                                 |

| ALU Operation                                       | 2–5                                                                                                                                                                                                                                                                                                                 |

| ALU Operating Modes                                 | 2–6                                                                                                                                                                                                                                                                                                                 |

| Saturation Mode                                     | 2–6                                                                                                                                                                                                                                                                                                                 |

| Floating-Point Rounding Modes                       | 2–6                                                                                                                                                                                                                                                                                                                 |

|                                                     |                                                                                                                                                                                                                                                                                                                     |

|                                                     |                                                                                                                                                                                                                                                                                                                     |

| ALU Zero Flag (AZ)                                  | 2–8                                                                                                                                                                                                                                                                                                                 |

|                                                     |                                                                                                                                                                                                                                                                                                                     |

|                                                     | IEEE FLOATING-POINT OPERATIONS<br>Extended Floating-Point Precision (ADSP-21020 Only)<br>Floating-Point Exceptions<br>FIXED-POINT OPERATIONS<br>ROUNDING<br>ALU<br>ALU Operation<br>ALU Operating Modes<br>Saturation Mode<br>Floating-Point Rounding Modes<br>Floating-Point Rounding Boundary<br>ALU Status Flags |

| 2.5.3.3 |                                          | 2–8  |

|---------|------------------------------------------|------|

| 2.5.3.4 |                                          | 2-8  |

| 2.5.3.5 |                                          | 2-8  |

| 2.5.3.6 |                                          | 2–9  |

| 2.5.3.7 |                                          |      |

| 2.5.3.8 |                                          |      |

| 2.5.3.9 | Compare Accumulation                     | 2–9  |

| 2.5.4   | ALU Instruction Summary                  | 2–10 |

| 2.6     | MULTIPLIER                               | 2–11 |

| 2.6.1   | Multiplier Operation                     | 2–11 |

| 2.6.2   | Fixed-Point Results                      | 2–12 |

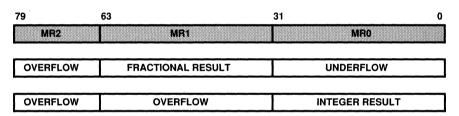

| 2.6.2.1 | MR Registers                             | 2–12 |

| 2.6.3   | Fixed-Point Operations                   | 2–13 |

| 2.6.3.1 | Clear MR Register                        |      |

| 2.6.3.2 |                                          | 2–14 |

| 2.6.3.3 |                                          |      |

| 2.6.4   | Floating-Point Operating Modes           |      |

| 2.6.4.1 | Floating-Point Rounding Modes            |      |

| 2.6.4.2 | ······································   | 2–15 |

| 2.6.5   | Multiplier Status Flags                  |      |

| 2.6.5.1 | Multiplier Underflow Flag (MU)           | 2–16 |

| 2.6.5.2 | ······································   |      |

| 2.6.5.3 | <b>J</b> ( <b>J</b> ( <b>J</b> )         |      |

| 2.6.5.4 | Multiplier Invalid Flag (MI)             |      |

| 2.6.6   | Multiplier Instruction Summary           |      |

| 2.7     | SHIFTER                                  |      |

| 2.7.1   | Shifter Operation                        |      |

| 2.7.2   | Bit Field Deposit & Extract Instructions |      |

| 2.7.3   | Shifter Status Flags                     |      |

| 2.7.3.1 | Shifter Zero Flag (SZ)                   | 2–24 |

| 2.7.3.2 |                                          |      |

| 2.7.3.3 |                                          |      |

| 2.7.4   | Shifter Instruction Summary              |      |

| 2.8     | MULTIFUNCTION COMPUTATIONS               |      |

| 2.9     | REGISTER FILE                            |      |

| 2.9.1   | Alternate (Secondary) Registers          | 2–28 |

|         |                                          |      |

### CHAPTER 3 PROGRAM SEQUENCING

| 3.1     | OVERVIEW                                       |

|---------|------------------------------------------------|

| 3.1.1   | Instruction Cycle                              |

| 3.1.2   | Program Sequencer Architecture                 |

| 3.1.2.1 | Program Sequencer Registers & System Registers |

| 3.2     | PROGRAM SEQUENCER OPERATIONS                   |

| 3.2.1   | Sequential Instruction Flow                    |

| 3.2.2   | Program Memory Data Access                     |

| 3.2.3   | Branches                                       |

| 3.2.4   | Loops                                          |

| 3.3     | CONDITIONAL INSTRUCTION EXECUTION              |

| 3.4     | BRANCHES (CALL, JUMP, RTS, RTI)                |

| 3.4.1   | Delayed And Nondelayed Branches                |

| 3.4.2   | PC Stack                                       |

| 3.5     | LOOPS                                          |

| 3.5.1   | Restrictions And Short Loops                   |

| 3.5.1.1 | General Restrictions                           |

| 3.5.1.2 | Counter-Based Loops                            |

| 3.5.1.3 | Non-Counter-Based Loops                        |

| 3.5.2   | Loop Address Stack                             |

| 3.5.3   | Loop Counters And Stack                        |

| 3.5.3.1 | CURLCNTR                                       |

| 3.5.3.2 | LCNTR                                          |

| 3.6     | INTERRUPTS                                     |

| 3.6.1   | Interrupt Latency                              |

| 3.6.2   | Interrupt Latch                                |

| 3.6.2.1 | Interrupt Priority                             |

| 3.6.2.2 | Software Interrupts                            |

| 3.6.3   | Interrupt Masking And Control                  |

| 3.6.3.1 | Interrupt Mask3-25                             |

| 3.6.3.2 | Interrupt Nesting & IMASKP                     |

| 3.6.4   | Status Stack                                   |

| 3.6.5   | External Interrupt Timing & Sensitivity        |

| 3.6.5.1 | Asynchronous External Interrupts               |

| 3.7     | STACK FLAGS                                    |

| 3.8     | IDLE                                           |

| 3.9     | INSTRUCTION CACHE                              |

| 3.9.1   | Cache Architecture3-30                         |

| 3.9.2   | Cache Efficiency3-32                           |

| 3.9.3   | Cache Enable And Cache Freeze3-32              |

### CHAPTER 4 DATA ADDRESSING

| 4.1     | OVERVIEW                            | 4–1  |

|---------|-------------------------------------|------|

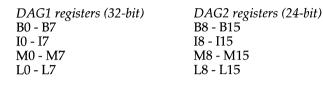

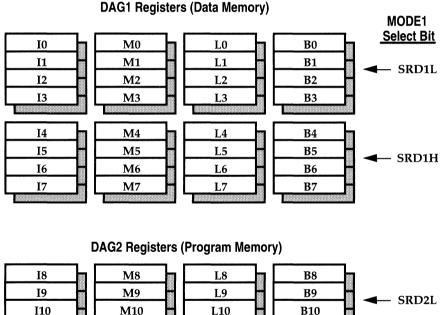

| 4.2     | DAG REGISTERS                       | 4–1  |

| 4.2.1   | Alternate DAG Registers             |      |

| 4.3     | DAG OPERATION                       |      |

| 4.3.1   | Address Output And Modification     | 4–4  |

| 4.3.1.1 | DAG Modify Instructions             |      |

| 4.3.1.2 | Immediate Modifiers                 |      |

| 4.3.2   | Circular Buffer Addressing          | 4–6  |

| 4.3.2.1 | Circular Buffer Operation           |      |

| 4.3.2.2 | Circular Buffer Registers           |      |

| 4.3.2.3 | Circular Buffer Overflow Interrupts | 4–8  |

| 4.3.3   | Bit-Reversal                        |      |

| 4.3.3.1 | Bit-Reverse Mode                    |      |

| 4.3.3.2 | Bit-Reverse Instruction             |      |

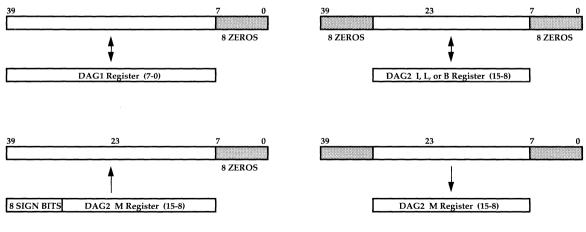

| 4.4     | DAG REGISTER TRANSFERS              | 4–10 |

| 4.4.1   | DAG Register Transfer Restrictions  | 4–11 |

|         |                                     |      |

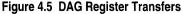

#### CHAPTER 5 TIMER

| 5.1   | OVERVIEW                   | -1 |

|-------|----------------------------|----|

| 5.2   | TIMER OPERATION            | -1 |

| 5.2.1 | Timer Enable And Disable5- | -1 |

| 5.2.2 | Timer Interrupt            | -4 |

|       | TIMER REGISTERS            |    |

### CHAPTER 6 MEMORY INTERFACE

|       |                                        | <b>.</b> . |

|-------|----------------------------------------|------------|

| 6.1   | MEMORY MANAGEMENT AND INTERFACE        | 6–1        |

| 6.2   | MEMORY BUSES AND CONTROL PINS          | 6–2        |

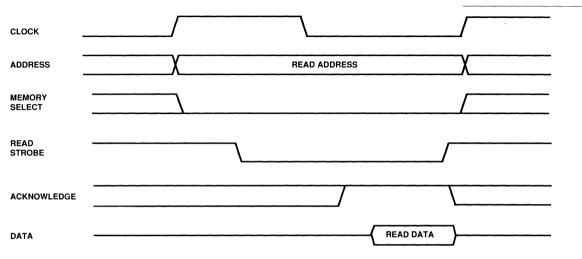

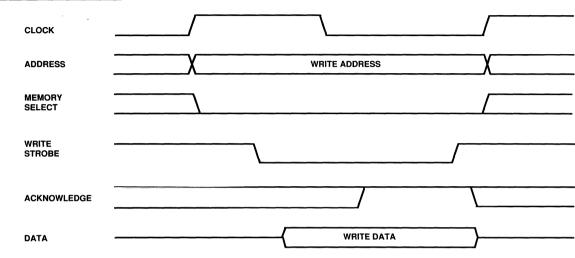

| 6.3   | MEMORY INTERFACE TIMING                | 6–4        |

| 6.3.1 | Memory Read                            |            |

| 6.3.2 | Memory Write                           |            |

| 6.3.3 | Three-State Controls                   |            |

| 6.4   | MEMORY BANKS                           | 6–8        |

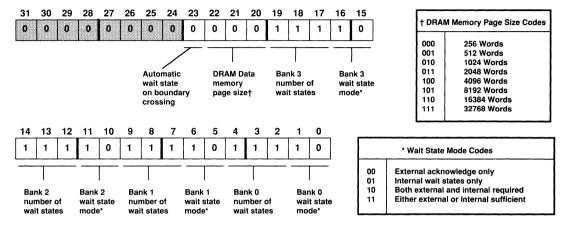

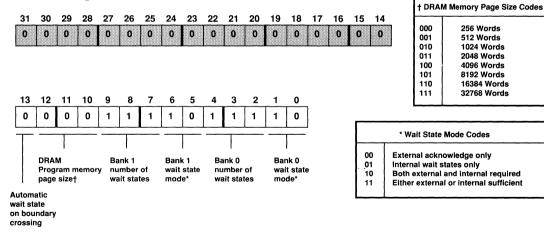

| 6.5   | WAIT STATES (EXTENDED MEMORY CYCLES)   | 6–9        |

| 6.5.1 | Extended Data Memory Address Hold Time |            |

| 6.6   | MEMORY PAGE BOUNDARY DETECTION         |            |

| 6.6.1 | Page Size                              |            |

| 6.6.2 | Wait States On Page Boundary Crossings |            |

| 6.7   | BUS REQUEST/BUS GRANT                  |            |

| 6.8   | BUS EXCHANGE (PX REGISTERS)            |            |

|       |                                        | • •        |

viii

### CHAPTER 7 INSTRUCTION SUMMARY

| 7.1     | OVERVIEW                                     |

|---------|----------------------------------------------|

| 7.2     | IMPORTANT PROGRAMMING REMINDERS              |

| 7.2.1   | Extra Cycle Conditions7-2                    |

| 7.2.1.1 | Nondelayed Branches7–2                       |

| 7.2.1.2 | Program Memory Data Access With Cache Miss   |

| 7.2.1.3 | Program Memory Data Access In Loops7-2       |

| 7.2.1.4 | One- And Two-Instruction Loops7–3            |

| 7.2.1.5 | DAG And Memory Control Register Writes7-4    |

| 7.2.1.6 | Wait States                                  |

| 7.2.1.7 | Page Boundary Crossing7-5                    |

| 7.2.1.8 | Three-State Enables7-5                       |

| 7.2.1.9 | Bus Request/Bus Grant7-5                     |

| 7.2.2   | Delayed Branch Restrictions7-5               |

| 7.2.3   | Loop Restrictions7–6                         |

| 7.2.4   | Interrupts7–6                                |

| 7.2.5   | IRPTL7-7                                     |

| 7.2.6   | Effect Latency And Read Latency7-7           |

| 7.2.7   | CURLCNTR Write & LCE7-8                      |

| 7.2.8   | Circular Buffer Initialization7–8            |

| 7.2.9   | Bit-Reverse Mode And Data Memory Bank Select |

| 7.2.10  | Disallowed DAG Register Transfers7-8         |

| 7.2.11  | Two Writes To Register File7–9               |

| 7.2.12  | Stack Status Flags7–9                        |

| 7.2.13  | Wait States And Three-State Enables7-9       |

| 7.2.14  | Computation Units7-9                         |

### CHAPTER 8 ASSEMBLY PROGRAMMING TUTORIAL

| 8.1     | INTRODUCTION                                   | 8–1  |

|---------|------------------------------------------------|------|

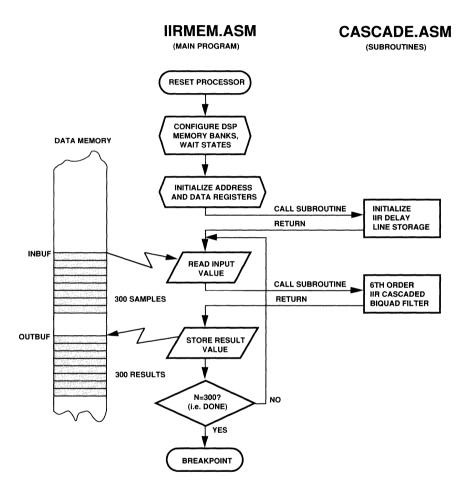

| 8.2     | EXAMPLE #1: DATA IN MEMORY, NO INTERRUPTS      | 8–2  |

| 8.2.1   | File Inventory                                 | 8–5  |

| 8.2.2   | Architecture Description File (generic.ach)    | 8–5  |

| 8.2.3   | External vs. Internal Address Decoding         | 8–7  |

| 8.2.4   | Specifying The .ACH File                       | 8–8  |

| 8.2.5   | Main Program (iirmem.asm)                      | 8–8  |

| 8.2.5.1 | Initial Setups: Initialization Following Reset | 8–11 |

| 8.2.5.2 | Main Processing Loop                           | 8–14 |

| 8.2.6   | Creating The Executable Program                | 8–15 |

| 8.2.7   | Simulation                                     | 8–15 |

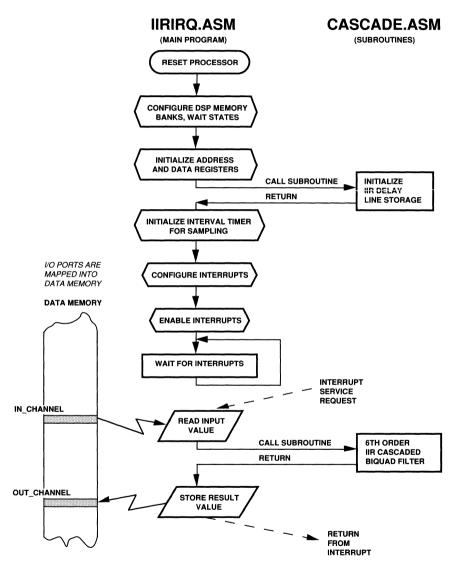

| 8.3     | EXAMPLE #2-INTERRUPT-DRIVEN, WITH PORT I/O             |      |

|---------|--------------------------------------------------------|------|

| 8.3.1   | File Inventory                                         |      |

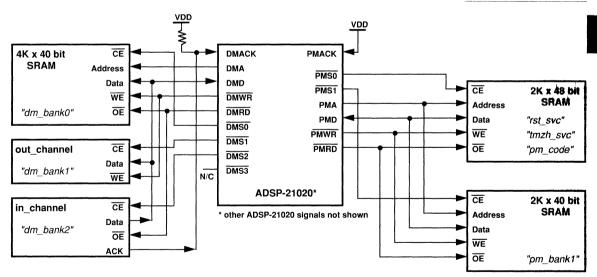

| 8.3.2   | Architecture Description File (iirirq.ach)             | 8–16 |

| 8.3.3   | Main Program (iirirq.asm)                              | 8–19 |

| 8.3.3.1 | Initialization Following Reset (Initial Setups)        |      |

| 8.3.3.2 | Main Processing Loop                                   |      |

| 8.3.3.3 | Terminating The Main Processing Loop                   | 8–29 |

| 8.3.4   | Creating The Executable Program                        |      |

| 8.3.5   | Simulation                                             |      |

| 8.4     | CALLED SUBROUTINES (cascade.asm)                       | 8–31 |

| 8.4.1   | Writing Looped Code                                    |      |

| 8.4.2   | Rolling Loops For More Efficient Code                  | 8–32 |

| 8.4.3   | Multifunction Instructions And Register Restrictions   | 8–34 |

| 8.5     | DEVELOPING THE IIR FILTER AND COEFFICIENTS             |      |

| 8.5.1   | Normalized b Coefficient Biquad Filter Design Method . |      |

| 8.5.2   | DSP Code Generation                                    |      |

| 8.5.3   | Coefficient Formatting                                 |      |

| 8.6     | PROGRAMMING HINTS                                      |      |

| 8.6.1   | System Considerations For Scoping                      |      |

| 8.6.2   | Delayed Branches                                       |      |

| 8.6.3   | Multifunction Instruction Coding                       |      |

| 8.7     | COMPLETE FFT EXAMPLE                                   |      |

|         |                                                        |      |

### CHAPTER 9 HARDWARE SYSTEM DESIGN

| 9.1     | OVERVIEW                        | .9–1 |

|---------|---------------------------------|------|

| 9.1.1   | Basic System Configuration      |      |

| 9.1.2   | More Complex Configurations     | .9–2 |

| 9.2     | CLOCKS & SYNCHRONIZATION        |      |

| 9.2.1   | Synchronization Delay           | .9–3 |

| 9.3     | POWERUP & RESET                 |      |

| 9.4     | RCOMP PIN                       |      |

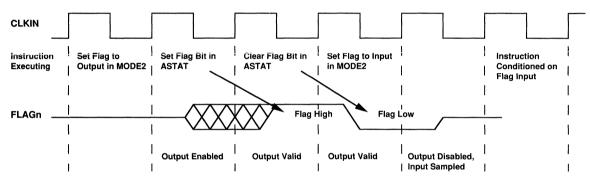

| 9.5     | FLAGS                           | 9–7  |

| 9.5.1   | Flag Direction                  | .9–7 |

| 9.5.2   | Flag Input                      | 9–7  |

| 9.5.3   | Flag Output                     | 9–8  |

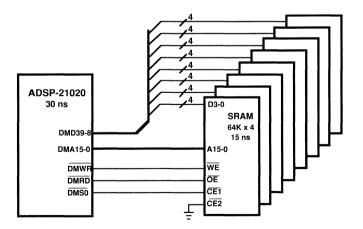

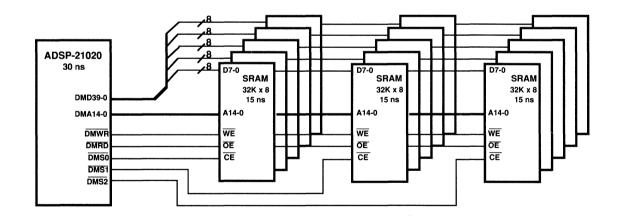

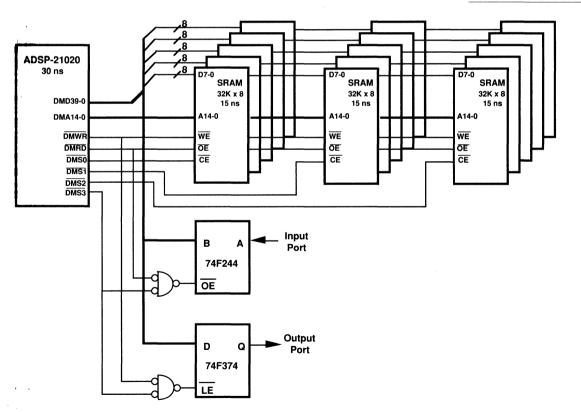

| 9.6     | MEMORY CONFIGURATIONS           | 9–8  |

| 9.6.1   | Single Processor Configurations | 9–8  |

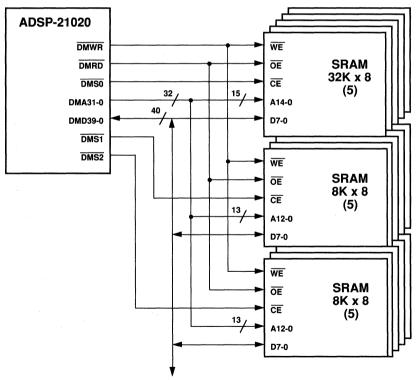

| 9.6.1.1 | One Memory Bank                 | 9–9  |

| 9.6.1.2 | Several Memory Banks            |      |

| 9.6.1.3 | Memory & I/O Devices            | 9–11 |

| 9.6.1.4 | Hardware Acknowledge            |      |

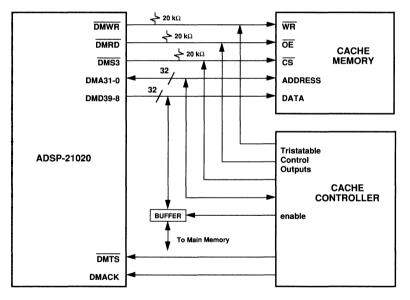

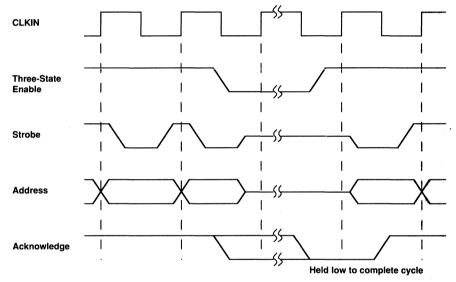

| 9.6.1.5  | Cache Memory                            | 9–13 |

|----------|-----------------------------------------|------|

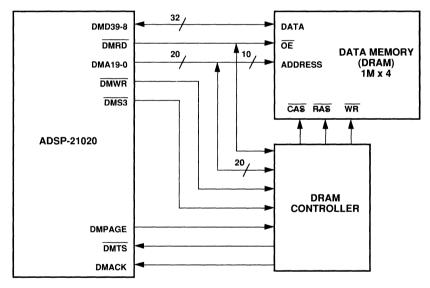

| 9.6.1.6  | DRAM With Paging                        | 9–14 |

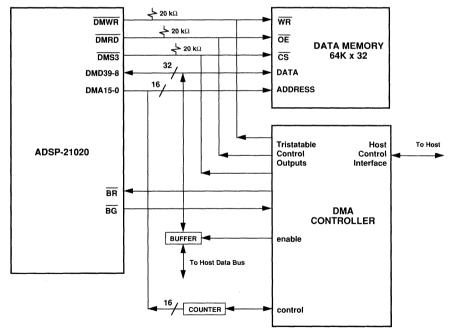

| 9.6.1.7  | Direct Memory Access (DMA)              | 9–16 |

| 9.6.2    | Multiprocessor Configurations           |      |

| 9.6.2.1  | Multiport Memory                        |      |

| 9.6.2.2  | Serial Data Flow                        |      |

|          | Buffer Latches                          | 9-20 |

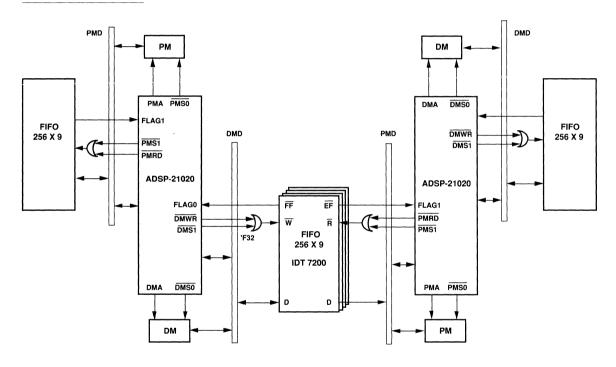

|          | FIFOs                                   | 9–22 |

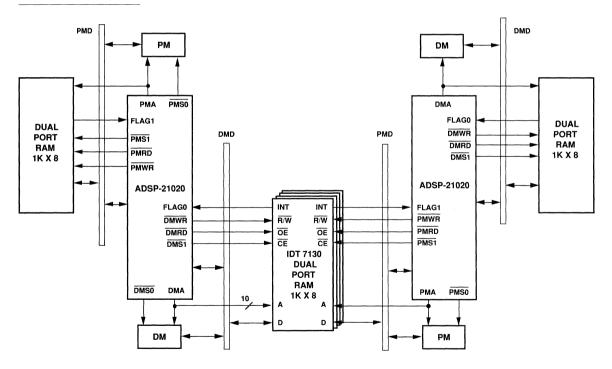

|          | Dual-Port Memory                        | 9–24 |

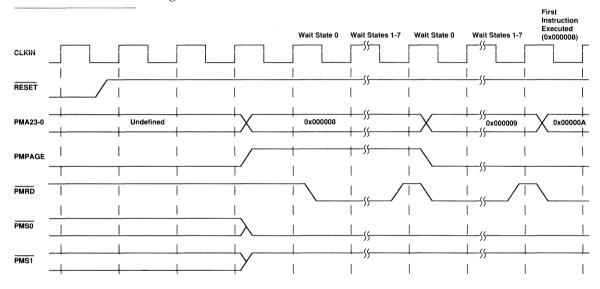

| 9.7      | PROGRAM MEMORY BOOT AT RESET            | 9–25 |

| 9.8      | MEMORY INTERFACE CAPACITIVE LOAD        | 9–27 |

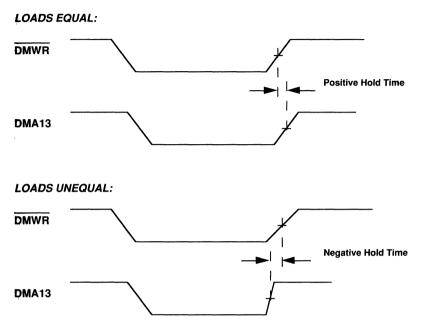

| 9.8.1    | Load Variations                         | 9–27 |

| 9.8.2    | Correcting The Timing                   | 9–29 |

| 9.9      | EZ-ICE EMULATOR CONSIDERATIONS          |      |

| 9.9.1    | Target Board Connector For EZ-ICE Probe |      |

| 9.9.2    | Other Hardware Considerations           |      |

| 9.10     | HOST PROCESSOR INTERFACE                |      |

| 9.10.1   | Data Transfer Sequences                 | 9–32 |

| 9.10.2   | Host Interface Code Examples            |      |

| 9.10.2.1 |                                         |      |

| 9.10.2.2 | · · · · · · · · · · · · · · · · · · ·   |      |

| 9.10.2.3 | B High Speed Transfers                  | 9–38 |

### APPENDIX A INSTRUCTION SET REFERENCE

| A.1<br>A.2<br>A.3<br>A.4<br>A.5 | OVERVIEW<br>INSTRUCTION SYNTAX NOTATION<br>OPCODE NOTATION<br>CONDITION CODES<br>UNIVERSAL REGISTERS | A-2<br>A-3<br>A-8 |

|---------------------------------|------------------------------------------------------------------------------------------------------|-------------------|

|                                 | GROUP I.<br>COMPUTE AND MOVE INSTRUCTIONS                                                            | A–11              |

|                                 | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                 |                   |

| GROUP II.<br>PROGRAM FLOW CONTROL                  | A–23 |

|----------------------------------------------------|------|

| direct jumplcall                                   | A–24 |

| indirect jumplcall / compute                       |      |

| return from subroutinelinterrupt / compute         |      |

| do until counter expired                           |      |

| do until                                           |      |

| GROUP III.                                         |      |

| IMMEDIATE MOVE                                     | A–33 |

| ureg $\leftrightarrow$ DMIPM (direct addressing)   | A–34 |

| ureg $\leftrightarrow$ DMIPM (indirect addressing) | A–35 |

| immediate data $\rightarrow$ DMIPM                 | A–36 |

| immediate data $ ightarrow$ ureg                   | A–37 |

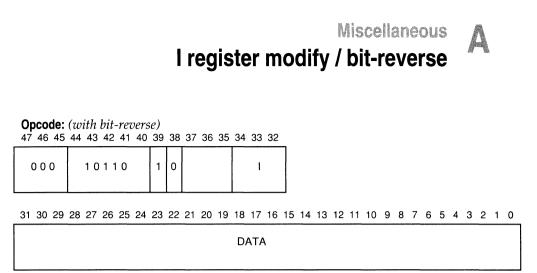

| GROUP IV.<br>MISCELLANEOUS                         | A–39 |

| system register bit manipulation                   | A–40 |

| I register modify / bit-reverse                    | A–42 |

| pushlpop stacks                                    | A–44 |

| nop                                                | A–45 |

| idle                                               |      |

### APPENDIX B COMPUTE OPERATION REFERENCE

| B.1   | OVERVIEW                   | B–1  |

|-------|----------------------------|------|

| B.2   | SINGLE-FUNCTION OPERATIONS | B–1  |

| B.2.1 | ALU Operations             | B–2  |

|       | Rn = Rx + Ry               | B–4  |

|       | Rn = Rx – Rý               |      |

|       | Rn = Rx + Ry + Cl          | B–6  |

|       | Rn = Rx – Ry + Cl – 1      |      |

|       | Rn = (Rx + Ŕy)/2           | B–8  |

|       | COMP(Rx, Ry)               | B–9  |

|       | Rn = Rx + Cl               | B–10 |

|       | Rn = Rx + Cl – 1           | B–11 |

|       | Rn = Rx + 1                | B–12 |

| Rn = Rx – 1                       | B-13 |

|-----------------------------------|------|

| Rn = –Rx                          | B–14 |

| Rn = ABS Rx                       | B–15 |

| Rn = PASS Rx                      |      |

| Rn = Rx AND Ry                    | B–17 |

| Rn = Rx OR Ry                     |      |

| Rn = Rx XOR Ry                    | B–19 |

| Rn = NOT Rx                       |      |

| Rn = MIN(Rx, Ry)                  |      |

| Rn = MAX(Rx, Ry)                  |      |

| Rn = CLIP Rx BY Ry                |      |

| Fn = Fx + Fy                      |      |

| Fn = Fx – Fy                      |      |

| Fn = ABS (Fx + Fy)                |      |

| Fn = ABS (Fx – Fy)                |      |

| Fn = (Fx + Fy)/2                  | B–28 |

| COMP(Fx, Fy)                      |      |

| Fn = –Fx                          |      |

| Fn = ABS Fx                       |      |

| Fn = PASS Fx                      |      |

| Fn = RND Fx                       |      |

| Fn = SCALB Fx BY Ry               |      |

| Rn = MANT Fx                      |      |

| Rn = LOGB Fx                      |      |

| Rn = FIX Fx BY Ry/Rn = FIX Fx     |      |

| Fn = FLOAT Rx BY Ry/Fn = FLOAT Rx |      |

| Fn = RECIPS Fx                    |      |

| Fn = RSQRTS Fx                    |      |

| Fn = Fx COPYSIGN Fy               |      |

| Fn = MIN(Fx, Fy)                  |      |

| Fn = MAX(Fx, Fy)                  |      |

| Fn = CLIP Fx BY Fy                |      |

| Multiplier Operations             |      |

| RnIMR = Rx * Ry                   |      |

| RnIMR = MR + Řx * Ry              | B–48 |

| RnIMR = MR - Rx * Ry              |      |

| RnIMR = SAT MR                    | B–50 |

| RnIMR = RND MR                    |      |

| MR = 0                            |      |

| MR=Rn / Rn=MR                     |      |

| Fn = Fx * Fy                      | B–53 |

B.2.2

B.2.3

| B.2.3 | Shifter Operations                                     | B–54 |

|-------|--------------------------------------------------------|------|

|       | Rn = LSHIFT Rx BY Ryl <data8></data8>                  |      |

|       | Rn = Rn OR LSHIFT Rx BY Ryl <data8></data8>            |      |

|       | Rn = ASHIFT Rx BY Ryl <data8></data8>                  |      |

|       | Rn = Rn OR ASHIFT Rx BY Ryl <data8></data8>            |      |

|       | Rn = ROT Rx BY RY  < data8>                            |      |

|       | Rn = BCLR Rx BY Ryl <data8></data8>                    | B60  |

|       | Rn = BSET Rx BY Ryl <data8></data8>                    | B–61 |

|       | Rn = BTGL Rx BY Ryl <data8></data8>                    | B62  |

|       | BTST Rx BY Ryl <data8></data8>                         | B–63 |

|       | Rn = FDEP Rx BY Ryl<br>bit6>: <len6></len6>            | B–64 |

|       | Rn = Rn OR FDEP Rx BY Ryl <bit6>:<len6></len6></bit6>  | B65  |

|       | Rn = FDEP Rx BY Ryl<br>bit6>: <len6> (SE)</len6>       | B–66 |

|       | Rn = Rn OR FDEP Rx BY Ryl<br>bit6>: <len6> (SE)</len6> | B67  |

|       | Rn = FEXT Rx BY Ryl <bit6>:<len6></len6></bit6>        |      |

|       | Rn = FEXT Rx BY Ryl <bit6>:<len6> (SE)</len6></bit6>   | B–69 |

|       | Rn = EXP Rx                                            |      |

|       | Rn = EXP Rx (EX)                                       |      |

|       | Rn = LEFTZ Rx                                          |      |

|       | Rn = LEFTO Rx                                          |      |

| B.2.4 | Multifunction Computations                             |      |

|       | Dual Add/Subtract (Fixed-Pt.)                          |      |

|       | Dual Add/Subtract (Floating-Pt)                        |      |

|       | Parallel Multiplier & ALU (Fixed-Pt.)                  |      |

|       | Parallel Multiplier & ALU (Floating-Pt.)               |      |

|       | Parallel Multiplier & Dual Add/Subtract                | B–80 |

#### APPENDIX C IEEE 1149.1 JTAG TEST ACCESS PORT

| C.1 | OVERVIEW                            | C–1  |

|-----|-------------------------------------|------|

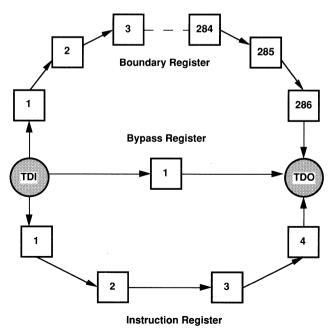

| C.2 | TEST ACCESS PORT                    | C–2  |

| C.3 | INSTRUCTION REGISTER                | C–2  |

| C.4 | BOUNDARY REGISTER                   | C–4  |

| C.5 | DEVICE IDENTIFICATION REGISTER      | C–11 |

| C.6 | BUILT-IN SELF-TEST OPERATION (BIST) | C–11 |

| C.7 | PRIVATE INSTRUCTIONS                |      |

| C.8 | REFERENCES                          | C–11 |

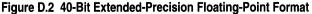

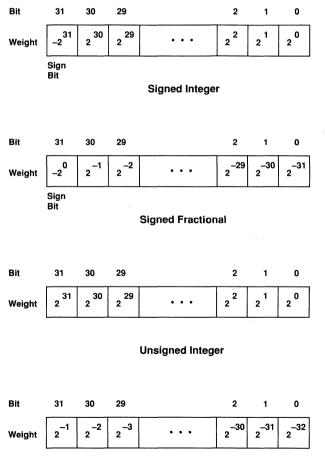

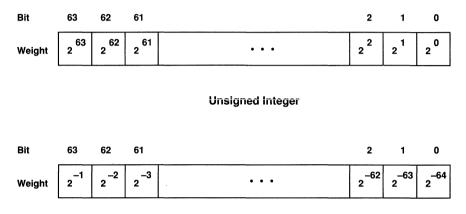

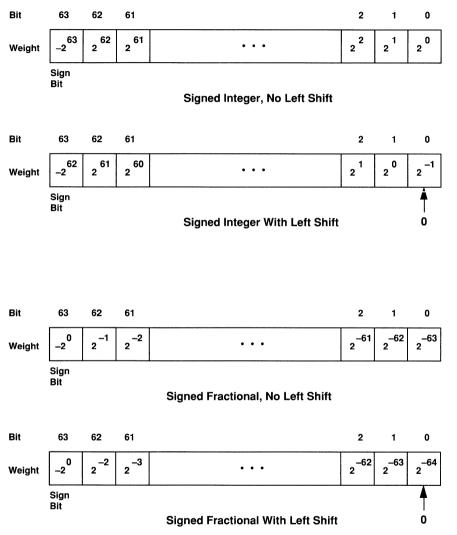

### APPENDIX D NUMERIC FORMATS

| D.1 | OVERVIEW                                         | D–1 |

|-----|--------------------------------------------------|-----|

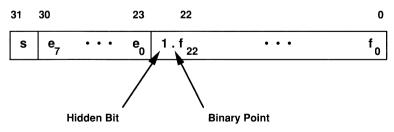

| D.2 | IEEE SINGLE-PRECISION FLOATING-POINT DATA FORMAT |     |

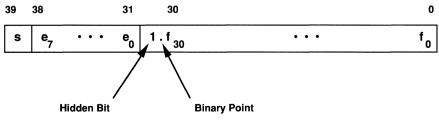

| D.3 | EXTENDED FLOATING-POINT FORMAT                   | D–2 |

| D.4 | FIXED-POINT FORMATS                              | D–3 |

### APPENDIX E CONTROL/STATUS REGISTERS

| E.1 OVERVIEW                                         | E–1  |

|------------------------------------------------------|------|

| E.2 SYSTEM REGISTERS                                 | E–1  |

| E.2.1 System Register Bit Operations                 | E–2  |

| E.2.1.1 Bit Test Flag                                | E–2  |

| E.2.2 User Registers                                 | E–2  |

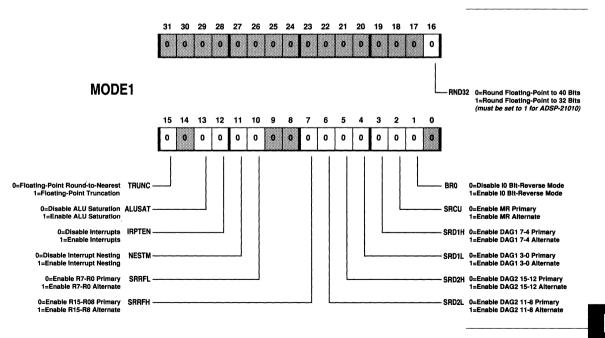

| E.3 MODE1 REGISTER                                   | E–3  |

| E.4 MODE2 REGISTER                                   | E–4  |

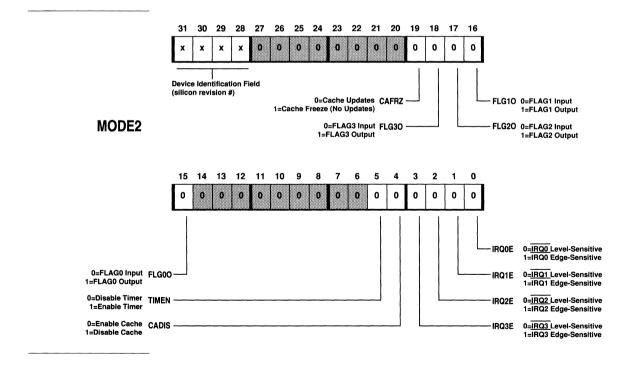

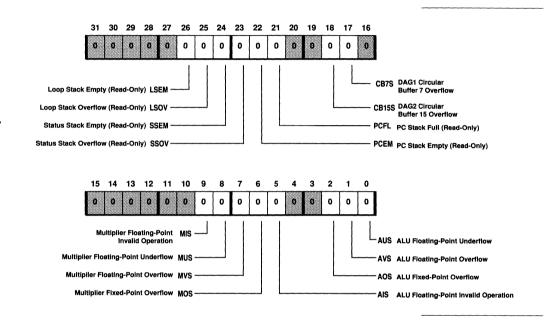

| E.5 ARITHMETIC STATUS REGISTER (ASTAT)               | E–5  |

| E.6 STICKY ARITHMETIC STATUS REGISTER (STKY)         | E–6  |

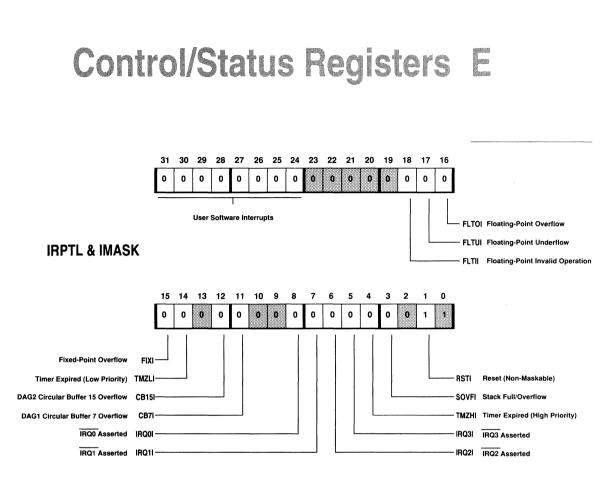

| E.7 INTERRUPT LATCH (IRPTL) & INTERRUPT MASK (IMASK) | E–8  |

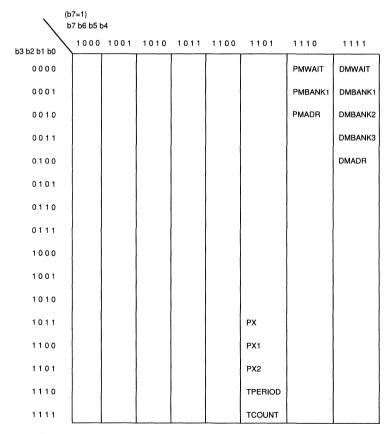

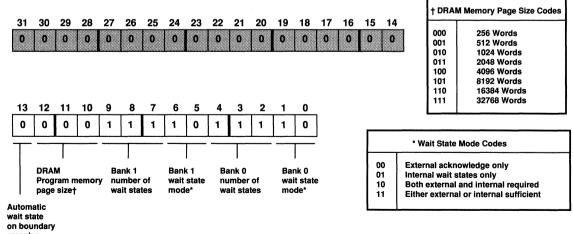

| E.8 PROGRAM MEMORY INTERFACE CONTROL (PMWAIT)        | E–10 |

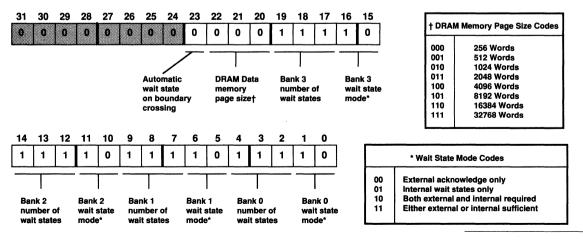

| E.9 DATA MEMORY INTERFACE CONTROL (DMWAIT)           | E–11 |

### **REVISIONS FOR 2ND EDITION**

### INDEX

### FIGURES

| Figure 1.1 | ADSP-21020 Block Diagram                         |      |

|------------|--------------------------------------------------|------|

| Figure 1.2 | Program Development                              |      |

| Figure 2.1 | Computation Units                                | 2–2  |

| Figure 2.2 | Multiplier Fixed-Point Result Placement          | 2–12 |

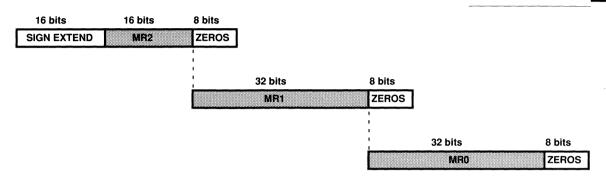

| Figure 2.3 | MR Transfer Formats                              | 2–13 |

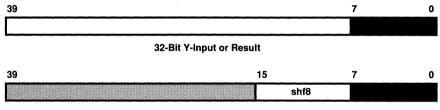

| Figure 2.4 | Register File Fields for Shifter Instructions    | 2–20 |

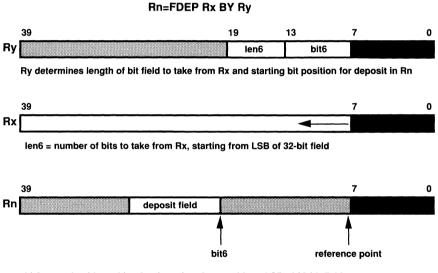

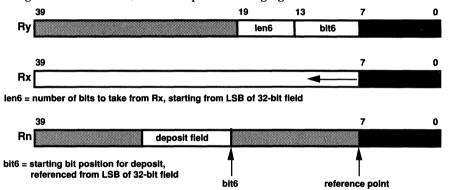

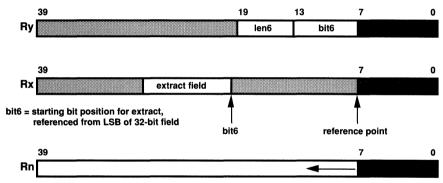

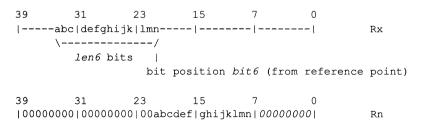

| Figure 2.5 | Register File Fields for FDEP, FEXT Instructions |      |

| Figure 2.6 | Bit Field Deposit Instruction                    |      |

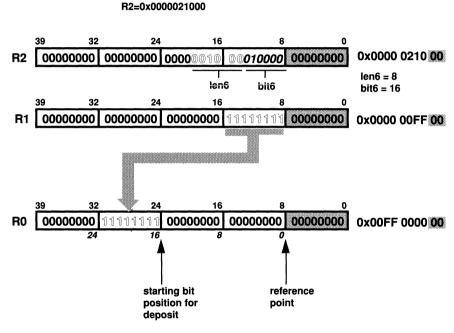

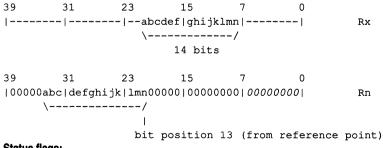

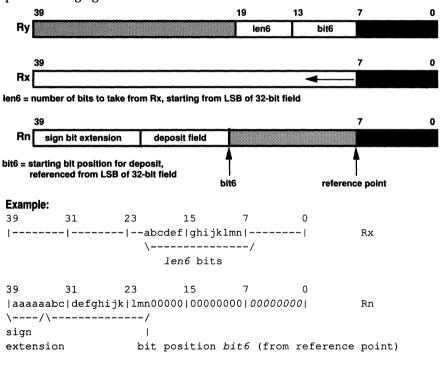

| Figure 2.7 | Bit Field Deposit Example                        |      |

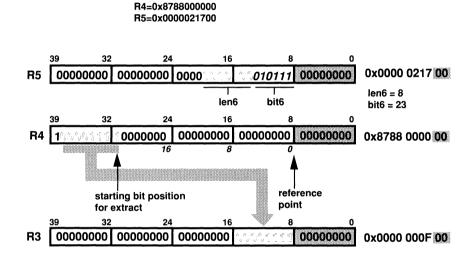

| Figure 2.8 | Bit Field Extract Example                        |      |

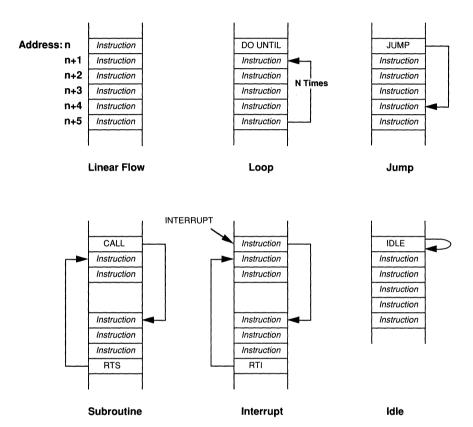

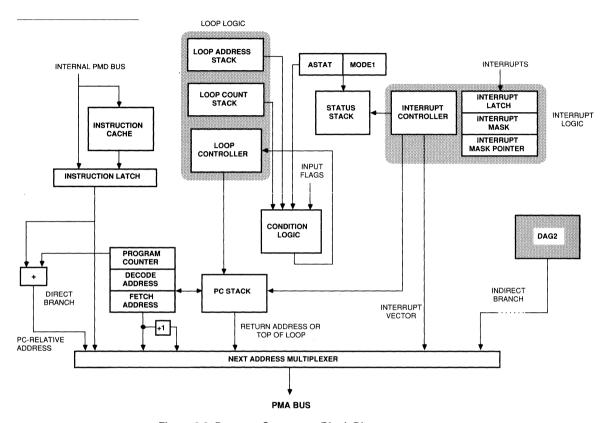

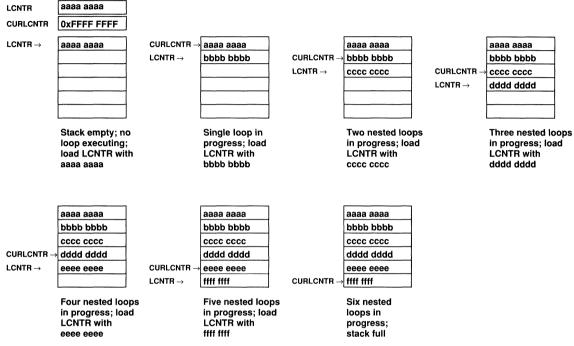

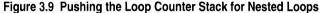

| Figure 3.1<br>Figure 3.2<br>Figure 3.3<br>Figure 3.4<br>Figure 3.5<br>Figure 3.6<br>Figure 3.7<br>Figure 3.8<br>Figure 3.9<br>Figure 3.10<br>Figure 3.11<br>Figure 3.12 | Program Flow Variations<br>Pipelined Execution Cycles<br>Program Sequencer Block Diagram<br>Nondelayed Branches<br>Delayed Branches<br>Loop Operation<br>One-Instruction Loops<br>Two-Instruction Loops<br>Pushing the Loop Counter Stack for Nested Loops<br>Interrupt Handling<br>Instruction Cache Architecture<br>Cache-Inefficient Code | 3–3<br>3–4<br>3–10<br>3–11<br>3–14<br>3–15<br>3–16<br>3–20<br>3–22<br>3–31 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

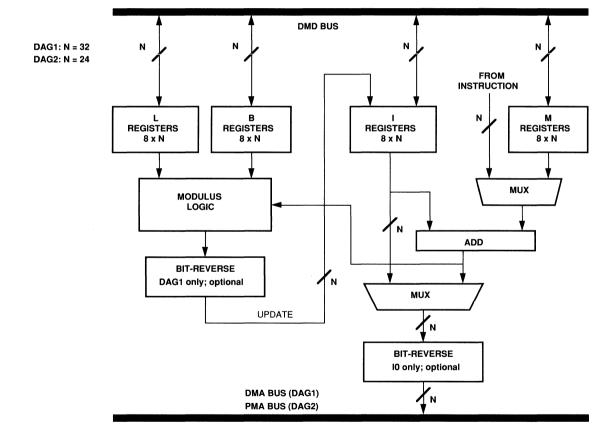

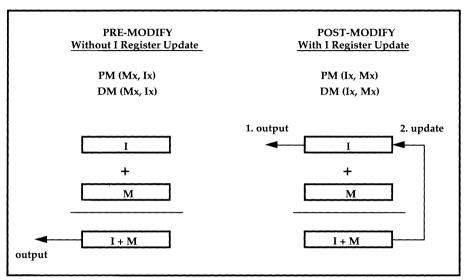

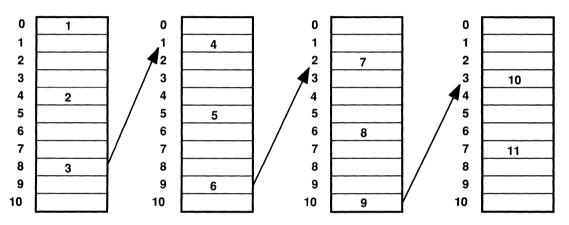

| Figure 4.1<br>Figure 4.2<br>Figure 4.3<br>Figure 4.4<br>Figure 4.5                                                                                                      | Data Address Generator Block Diagram<br>Alternate DAG Registers<br>Pre-Modify and Post-Modify Operations<br>Circular Data Buffers<br>DAG Register Transfers                                                                                                                                                                                  | 4–3<br>4–5<br>4–7                                                          |

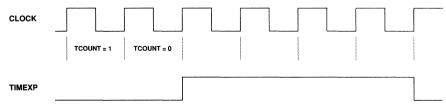

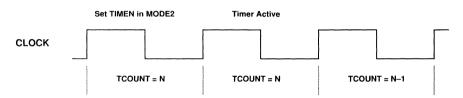

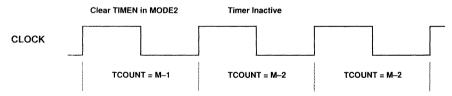

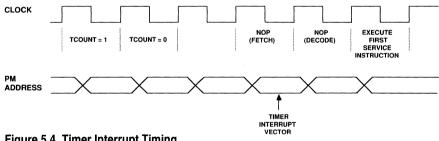

| Figure 5.1<br>Figure 5.2<br>Figure 5.3<br>Figure 5.4                                                                                                                    | Timer Block Diagram<br>TIMEXP Signal<br>Timer Enable and Disable<br>Timer Interrupt Timing                                                                                                                                                                                                                                                   | 5–2<br>5–3                                                                 |

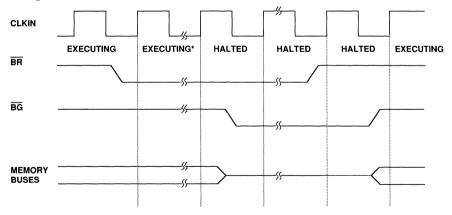

| Figure 6.1<br>Figure 6.2<br>Figure 6.3<br>Figure 6.4<br>Figure 6.5                                                                                                      | Memory Read Cycle<br>Memory Write Cycle<br>Wait State Control Registers<br>Bus Request/Bus Grant Timing<br>PX Register Transfers                                                                                                                                                                                                             | 6–6<br>6–11<br>6–14                                                        |

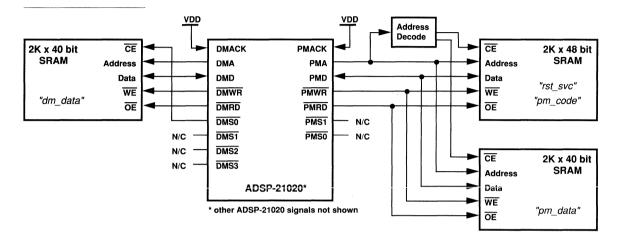

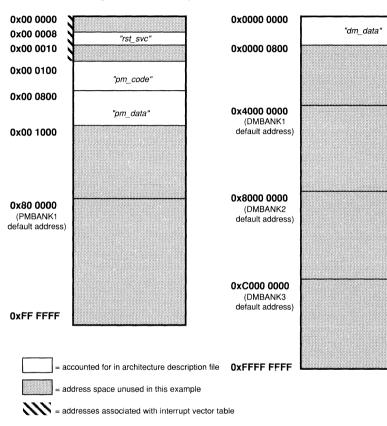

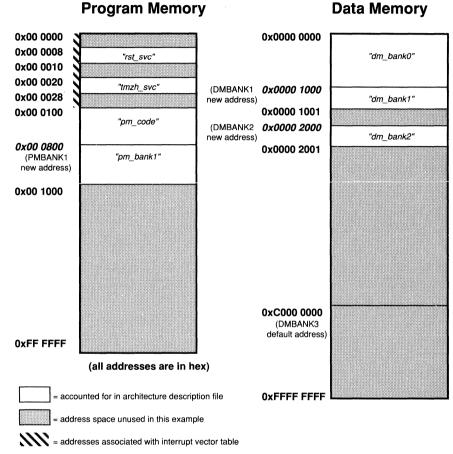

| Figure 8.1<br>Figure 8.2<br>Figure 8.3<br>Figure 8.4<br>Figure 8.5<br>Figure 8.6<br>Figure 8.7<br>Figure 8.8                                                            | Program Flow for First Example<br>Program Flow for Second Example<br>Physical Memory Architecture Described in "generic.ach"<br>Memory Map Described in "generic.ach"<br>Physical Memory Architecture Described in "iirirq.ach"<br>Memory Map Described in "iirirq.ach"<br>Filling and Draining the Pipeline<br>Loop Code Before Rolling     | 8–4<br>8–8<br>8–9<br>8–17<br>8–18<br>8–33                                  |

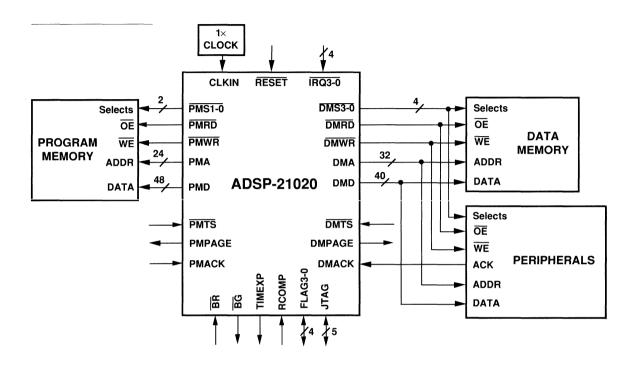

| Figure 9.1<br>Figure 9.2<br>Figure 9.3<br>Figure 9.4<br>Figure 9.5                                                                                                      | Basic ADSP-21020 System Configuration<br>Program Memory Interface Timing at Reset<br>Flag Output Timing<br>Interface to Single Data Memory Bank<br>Interface to Three Data Memory Banks                                                                                                                                                      | 9–6<br>9–8<br>9–9                                                          |

| Figure 9.6  | Interface to Three Data Memory Banks and Two I/O Devices   | 9–11 |

|-------------|------------------------------------------------------------|------|

| Figure 9.7  | I/O Device Interface with Hardware Acknowledge             | 9–12 |

| Figure 9.8  | Cache Memory Interface                                     | 9–13 |

| Figure 9.9  | Timing on Cache Miss                                       |      |

| Figure 9.10 | Page-Mode DRAM Interface                                   |      |

| Figure 9.11 | DMA Controller Interface Using Bus Request                 |      |

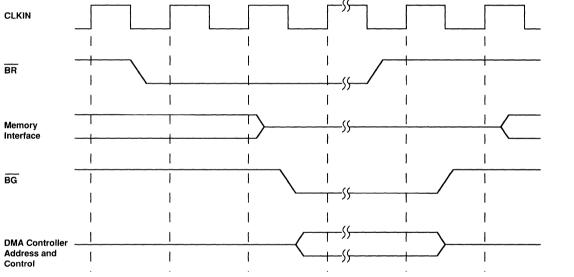

| Figure 9.12 | Bus Request Timing for DMA                                 |      |

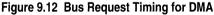

| Figure 9.13 | Four-Port RAM Configuration                                |      |

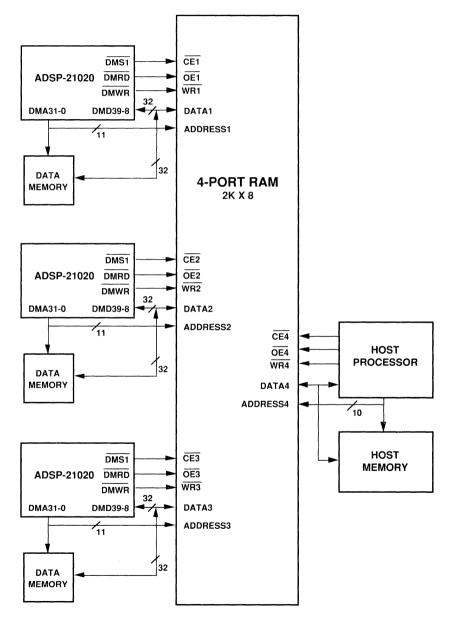

| Figure 9.14 | Serial Data Flow Using Buffers                             | 9–20 |

| Figure 9.15 | Serial Data Flow Using FIFOs                               |      |

| Figure 9.16 | Serial Data Flow Using Dual-Port RAM                       | 9–24 |

| Figure 9.17 | Example Loader Program                                     | 9–26 |

| Figure 9.18 | Memory Configuration with Unequal Capacitive Loads         | 9–28 |

| Figure 9.19 | Effect of Unequal Capacitive Loads                         |      |

| Figure 9.20 | Target Board Connector For EZ-ICE Probe (jumpers in place) | 9–31 |

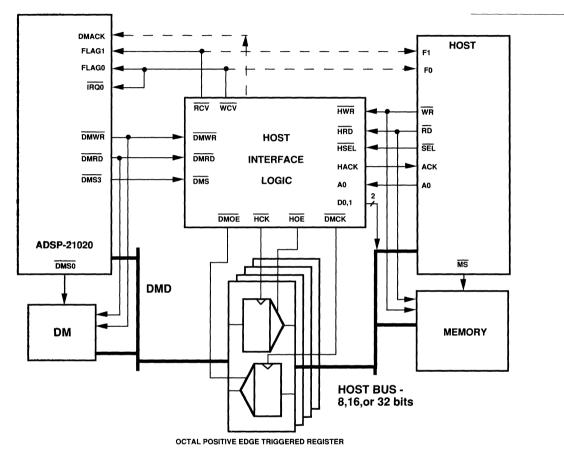

| Figure 9.21 | Host Interface Block Diagram                               | 9–33 |

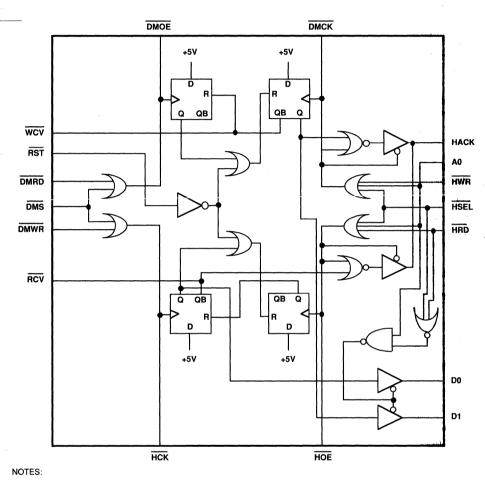

| Figure 9.22 | Host Interface Logic                                       | 9–34 |

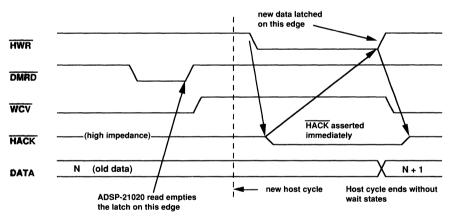

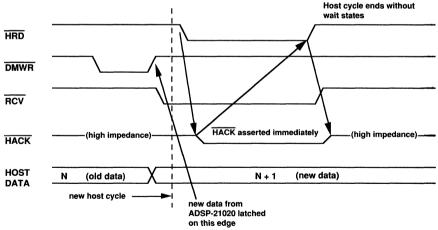

| Figure 9.23 | Host Write Timing                                          |      |

| Figure 9.24 | Host Read Timing                                           | 9–36 |

|             |                                                            |      |

| Figure A.1  | Map 1 Universal Register Addresses                         |      |

| Figure A.2  | Map 2 Universal Register Addresses                         | A–10 |

|             |                                                            |      |

| Figure C.1  | Serial Scan Paths                                          | C–3  |

|             |                                                            |      |

| Figure D.1  | IEEE 32-Bit Single-Precision Floating-Point Format         |      |

| Figure D.2  | 40-Bit Extended-Precision Floating-Point Format            |      |

| Figure D.3  | 32-Bit Fixed-Point Formats                                 |      |

| Figure D.4  | 64-Bit Unsigned Fixed-Point Product                        |      |

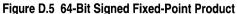

| Figure D.5  | 64-Bit Signed Fixed-Point Product                          | D–5  |

|             |                                                            |      |

### TABLES

| Table 3.1 | Program Sequencer Registers & System Registers |      |

|-----------|------------------------------------------------|------|

| Table 3.2 | Condition Codes                                |      |

| Table 3.3 | Interrupt Vectors and Priority                 |      |

| Table 3.4 | States of Outputs During IDLE                  |      |

| T-61-74   | Ountry Natation Occurrentians                  | 7 40 |

| Table 7.1 | Syntax Notation Conventions                    |      |

| Table 7.2 | Condition and Termination Codes                | 7–11 |

| Table 7.3 | Universal Registers and System Registers       | 7–12 |

| Table 7.4 | ALU Instructions                               | 7–13 |

| Table 7.5<br>Table 7.6<br>Table 7.7<br>Table 7.8                                        | Multiplier Instructions<br>Shifter and Shifter Immediate Instructions<br>Multifunction Instructions<br>Interrupt Vectors and Priority                                                                    | 7–15<br>7–16                        |

|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| Table 8.1<br>Table 8.2<br>Table 8.3                                                     | Files Used for Memory-Based (No Interrupts) Program<br>Files Used for Interrupt-Driven Program using Port I/O<br>Interrupt-Related Registers                                                             | 8–16                                |

| Table 9.1<br>Table 9.2                                                                  | ADSP-21020 Register Values After Reset<br>ADSP-21020 Pin States During Reset (while RESET=0)                                                                                                             | 9–5<br>9–6                          |

| Table B.1<br>Table B.2<br>Table B.3<br>Table B.4<br>Table B.5<br>Table B.6<br>Table B.7 | Fixed-Point ALU Operations<br>Floating-Point ALU Operations<br>Multiplier Operations<br>Multiplier Mod2 Options<br>Multiplier Mod1 Options<br>Shifter Operations<br>Parallel Multiplier/ALU Computations | B–3<br>B–45<br>B–46<br>B–46<br>B–54 |

| Table C.1                                                                               | Test Instructions                                                                                                                                                                                        | C–3                                 |

| Table D.1                                                                               | IEEE Single-Precision Floating-Point Data Types                                                                                                                                                          | D–2                                 |

| Table E.1                                                                               | System Registers                                                                                                                                                                                         | E–1                                 |

### LISTINGS

| Listing 8.1  | generic.ach                                             |      |

|--------------|---------------------------------------------------------|------|

| Listing 8.2  | iirmem.asm                                              |      |

| Listing 8.3  | iirirg.ach                                              |      |

| Listing 8.4  | iirirg.asm                                              |      |

| Listing 8.5  | def21020.h                                              |      |

| Listing 8.6  | Input Data Read by Input Port (Normalized Unit Impulse) |      |

| Listing 8.7  | Output Data Stored by Output Port (Impulse Response)    |      |

| Listing 8.8  | Final Rolled Loop Example in "cascade.asm"              | 8–34 |

| Listing 8.9  | FDAS File                                               |      |

| Listing 8.10 | "iircoefs.dat" File                                     | 8–36 |

|              |                                                         |      |

# Introduction **II** 1

#### 1.1 **GENERAL DESCRIPTION**

The ADSP-21020 and ADSP-21010 are the two members of Analog Devices' ADSP-21000 family of floating-point digital signal processors (DSPs). The ADSP-21000 family architecture further addresses the five central requirements for DSPs established in the ADSP-2100 family of 16bit fixed-point DSPs:

- Fast, flexible arithmetic computation units •

- Unconstrained data flow to and from the computation units

- Extended precision and dynamic range in the computation units

- Dual address generators

- Efficient program sequencing

Fast, Flexible Arithmetic. The ADSP-21020/21010 executes all instructions in a single cycle. It provides both one of the fastest cycle times available and the most complete set of arithmetic operations, including Seed 1/X, Seed  $1/\sqrt{X}$ , Min, Max, Clip, Shift and Rotate, in addition to the traditional multiplication, addition, subtraction and combined addition/ subtraction. It is IEEE floating-point compatible and allows either interrupt on arithmetic exception or latched status exception handling.

Unconstrained Data Flow. The ADSP-21020/21010 has a Harvard architecture combined with a 10-port data register file. In every cycle:

- Two operands can be read or written off-chip to or from the register file.

- Two operands can be supplied to the ALU,

- Two operands can be supplied to the multiplier, and

- Two results can be received from the ALU and multiplier (three, if the ALU operation is a combined addition/subtraction).

The processors' 48-bit orthogonal instruction word supports fully parallel data transfer and arithmetic operations in the same instruction.

**40-Bit Extended Precision**. The ADSP-21020 and ADSP-21010 handle 32-bit IEEE floating-point format as well as 32-bit integer and fractional formats (twos-complement and unsigned), while the ADSP-21020 also handles extended-precision 40-bit IEEE floating-point format. The ADSP-21020 carries extended precision throughout its computation units, limiting intermediate data truncation errors. When working with data on-chip, the extended-precision 32-bit mantissa can be transferred to and from all computation units. The 40-bit data bus may be extended off-chip as desired. The fixed-point formats have an 80-bit accumulator for true 32-bit fixed-point computations.

**Dual Address Generators**. The ADSP-21020/21010 has two data address generators (DAGs) that provide immediate or indirect (pre- and post-modify) addressing. Modulus and bit-reverse operations are supported with no constraints on buffer placement.

**Efficient Program Sequencing**. In addition to zero-overhead loops, the ADSP-21020/21010 supports single-cycle setup and exit for loops. Loops are both nestable (six levels in hardware) and interruptable. The processor supports both delayed and non-delayed branches.

#### 1.1.1 Key Enhancements

The ADSP-21000 family enhances the core DSP architecture to enable easier system development. The enhancements occur in four key areas:

- Architectural features for high-level language and operating system support.

- Access to serial scan path (IEEE 1149.1 compatible) and on-chip emulation features.

- Support of IEEE floating-point formats.

- Open memory system.

**High Level Languages**. The ADSP-21000 family architecture has several features which directly support high-level language compilers and operating systems:

- General purpose data and address register files,

- 32-bit native data types,

- Large address spaces (16M words in program memory, 4G words in data memory),

- Pre- and post-modify addressing,

- Unconstrained circular buffer placement, and

- On-chip program, loop, and interrupt stacks.

Additionally, the ADSP-21000 family architecture is designed specifically to support ANSI standard Numerical C—the first compiled language to support vector data types and operators for numeric and signal processing.

**Serial Scan and Emulation Features**. The ADSP-21020/21010 supports the IEEE-standard P1149 Joint Test Action Group (JTAG) standard for system test. This standard defines a method for serially scanning the I/O status of each component in a system. This serial port is also used to gain access to the ADSP-21020/21010 on-chip emulation features.

**IEEE Formats**. The ADSP-21020/21010 supports IEEE floating-point data formats. This means that algorithms developed on IEEE-compatible processors and workstations are portable across processors without concern for possible instability introduced by biased rounding or inconsistent error handling.

**Open Memory System**. No on-chip memory is included on the ADSP-21020/21010 (aside from a high-performance cache) specifically to avoid artificially constraining the development and upgrade of floating-point signal processing applications. This approach also facilitates the use of high-level languages and multitasking operating systems.

### 1.1.2 Why Floating-Point?

A processor's data format determines its ability to handle signals of differing precision, dynamic range, and signal-to-noise ratios. However, ease-of-use and time-to-market considerations are often equally important.

**Precision**. The precision of converters has been increasing and will continue to increase. In the past several years, average precision requirements have increased by 3 bits. A 20-bit audio A/D converter is now available from Analog Devices, and the trend is for both precision and sampling rates to increase.

**Dynamic Range**. Compression and decompression algorithms have traditionally operated on signals of known bandwidth. These algorithms were developed to behave regularly, to keep costs down and implementations easy. Increasingly, however, the trend in algorithm development is not to constrain the regularity and dynamic range of intermediate results. Adaptive filtering and imaging are two applications requiring wide dynamic range.

**Signal-to-Noise Ratio**. Radar, sonar and even commercial applications like speech recognition require wide dynamic range in order to discern selected signals from noisy environments.

**Ease-of-Use**. In general, floating-point digital signal processors are easier to use and allow a quicker time-to-market than processors that do not support floating-point formats. The extent to which this is true depends on the floating-point processor's architecture. Consistency with IEEE workstation simulations and the elimination of scaling are two clear ease-of-use advantages. High-level language programmability, large address spaces, and wide dynamic range allow system development time to be spent on algorithms and signal processing problems rather than assembly coding, code paging, and error handling.

#### 1.1.3 Future Product Migration Path

Analog Devices offers the ADSP-21000 family architecture as the highest performance for signal processing applications. Future processors based on this architecture will offer higher speed and feature integration, incorporating both internal memory and I/O peripherals on-chip.

### 1.2 ARCHITECTURE OVERVIEW

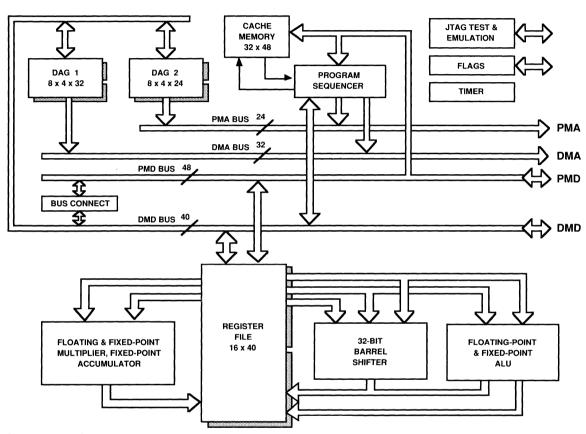

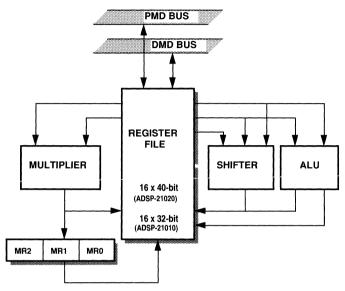

The following sections summarize the basic features of the ADSP-21020/21010 architecture. These features are described in more detail in succeeding chapters. Figure 1.1 shows a block diagram of the ADSP-21020 with it's 40-bit data paths.

#### 1.2.1 Computation Units

The ADSP-21020/21010 contains three independent computation units: an ALU, a multiplier with fixed-point accumulator, and a shifter. For meeting a wide variety of processing needs, the computation units process data in three formats: 32-bit fixed-point, 32-bit floating-point and 40-bit floating-point (ADSP-21020 only). The floating-point operations are single-precision IEEE-compatible. The 32-bit floating-point format is the standard IEEE format, whereas the 40-bit IEEE extended-precision format has eight more LSBs of mantissa for additional accuracy.

The ALU performs a standard set of arithmetic and logic operations in both fixed-point and floating-point formats. The multiplier performs floating-point and fixed-point multiplication as well as fixed-point multiply/add and multiply/subtract operations. The shifter performs logical and arithmetic shifts, bit manipulation, field deposit and extraction and exponent derivation operations on 32-bit operands.

Figure 1.1 ADSP-21020 Block Diagram

The computation units perform single-cycle operations; there is no computation pipeline. The units are connected in parallel rather than serially. The output of any unit may be the input of any unit on the next cycle. In a *multifunction* computation, the ALU and multiplier perform independent simultaneous operations. A 10-port register file is used for transferring data between the computation units and the data buses, and for storing intermediate results. The register file has two sets (primary and alternate) of sixteen registers each, for fast context switching. The registers are 32 bits wide on the ADSP-21010 and 40 bits wide on the ADSP-21020.

### 1.2.2 Address Generators And Program Sequencer

Two dedicated address generators and a program sequencer supply addresses for memory accesses. Together the sequencer and data address generators allow computational operations to execute with maximum efficiency because the computation units can be devoted exclusively to processing data. Because of its instruction cache, the ADSP-21020/21010 can simultaneously fetch an instruction and access data in both program memory and data memory.

The data address generators (DAGs) provide memory addresses when external memory data is transferred over the parallel memory ports to or from internal registers. Dual data address generators enable the processor to output simultaneous addresses for dual operand reads and writes. DAG1 supplies 32-bit addresses to data memory. DAG2 supplies 24-bit addresses to program memory for program memory data accesses.

Each DAG keeps track of up to eight address pointers, eight modifiers and eight length values. A pointer used for indirect addressing can be modified by a value in a specified register, either before (pre-modify) or after (post-modify) the access. A length value may be associated with each pointer to implement automatic modulo addressing for circular buffers, which can be located on arbitrary boundaries. Each DAG register has an alternate register that can be activated for fast context switching.

The program sequencer supplies instruction addresses to the program memory. It controls loop iterations and evaluates conditional instructions. With an internal loop counter and loop stack, the ADSP-21020/21010 executes looped code with zero overhead. No explicit jump instructions are required to loop or to decrement and test the counter.

The ADSP-21020/21010 achieves its fast program execution rate by means of pipelined *fetch*, *decode* and *execute* cycles. External memories have more time to complete an access than if there were no decode cycle; consequently, ADSP-21020/21010 systems can be built using slower and therefore less expensive memories.

The program sequencer includes a 32-word instruction cache. The cache allows the ADSP-21020/21010 to perform a program memory data access and execute the corresponding instruction in the same cycle, without any delay. The program sequencer fetches the instruction from the cache instead of program memory so that the processor can simultaneously access data in program memory. Only the instructions whose fetches conflict with program memory data accesses are cached.

1-6

### 1.2.3 Interrupts

The ADSP-21020/21010 has five external hardware interrupts (four general-purpose interrupts and a special interrupt for reset), nine internally generated interrupts and eight software interrupts. For the general-purpose external interrupts and the internal timer interrupt, the processor automatically stacks the arithmetic status and mode (MODE1) registers in parallel with servicing the interrupt, allowing four nesting levels of very fast service for these interrupts.

### 1.2.4 Timer

The programmable interval timer provides periodic interrupt generation. When enabled, the timer decrements a 32-bit count register every cycle. When this count register reaches zero, the ADSP-21020/21010 generates an interrupt and asserts its TIMEXP output. The count register is automatically reloaded from a 32-bit period register and the count resumes immediately.

### 1.2.5 Memory Buses And Interface

The external memory interface supports memory-mapped peripherals and slower memories with a user-defined combination of programmable wait states and hardware acknowledge signals. Both program memory and data memory addressing support page mode addressing of static column DRAMs.

The processor has four internal buses: the program memory address (PMA) and data memory address (DMA) buses are used for the addresses associated with program and data memory. The program memory data (PMD) and data memory data (DMD) buses are used for the data associated with the memory spaces. These buses are extended off chip. The DMS and PMS signals select data memory and program memory, respectively.

The program memory address (PMA) bus is 24 bits wide allowing direct access of up to 16M words of mixed instruction code and data. The program memory data (PMD) bus is 48 bits wide to accommodate the 48-bit instruction width. Fixed-point and single-precision floating-point data is aligned to the upper 32 bits of the PMD bus.

The data memory address (DMA) bus is 32 bits wide allowing direct access of up to 4G words of data. The data memory data (DMD) bus is 40 bits wide on the ADSP-21020 and 32 bits wide on the ADSP-21010. On the ADSP-21020, fixed-point and single-precision floating-point data is aligned to the upper 32 bits of the DMD bus. The DMD bus provides a

1 – 7

path for the contents of any register in the processor to be transferred to any other register or to any external data memory location in a single cycle. The data memory address comes from two sources: an absolute value specified in the instruction code (direct addressing) or the output of a data address generator (indirect addressing).

External devices can gain control of memory buses from the ADSP-21020/21010 with bus request/grant signals (BR and BG). To grant its buses in response to a bus request, the ADSP-21020/21010 halts internal operations and places its program and data memory interfaces in a high-impedance state. In addition, three-state controls (DMTS and PMTS) allow an external device to place either program or data memory interface in a high-impedance state without affecting the other interface and without halting the processor unless it requires a program memory access.

### 1.2.6 Internal Data Transfers

Nearly every internal register of the ADSP-21020/21010 is classified as a *universal register*. ADSP-21020/21010 instructions provide for transferring data between any two universal registers or between a universal register and external memory. This includes control registers and status registers, as well as the data registers in the register file.

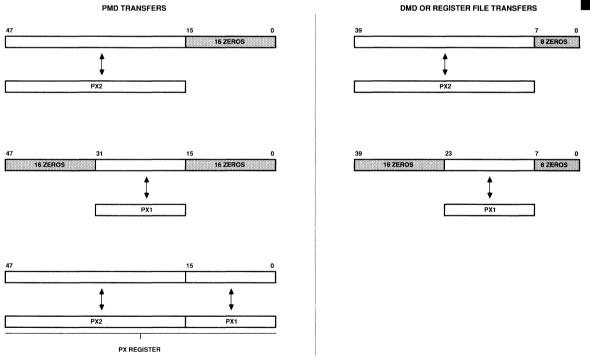

The PX registers permit data to be passed between the 48-bit PMD bus and the 40-bit DMD bus or between the 40-bit register file and the PMD bus. These registers contain hardware to handle the 8-bit width difference.

### 1.2.7 Context Switching

Many of the processor's registers have alternate registers that can be activated during interrupt servicing to facilitate a fast context switch. The data registers in the register file, DAG registers and the multiplier result register all have alternates. Registers active at reset are called *primary* registers, and the others are *alternate* registers. Bits in a mode control register determine the registers that are active at any particular time.

### 1.2.8 Instruction Set

The ADSP-21000 family instruction set provides a wide variety programming capabilities. *Multifunction* instructions enable computations in parallel with data transfers, as well as simultaneous multiplier and ALU operations. The addressing power of the ADSP-21020/21010 gives you flexibility in moving data both internally and externally. Every instruction can be executed in a single processor cycle. The ADSP-21000 family assembly language uses an algebraic syntax for ease of coding and readability. A comprehensive set of development tools supports program development.

### 1.3 DEVELOPMENT SYSTEM

The ADSP-21020/21010 is supported with a complete set of software and hardware development tools. The ADSP-21000 Family Development System includes software tools for programming and debugging as well as in-circuit emulators for system integration and debugging.

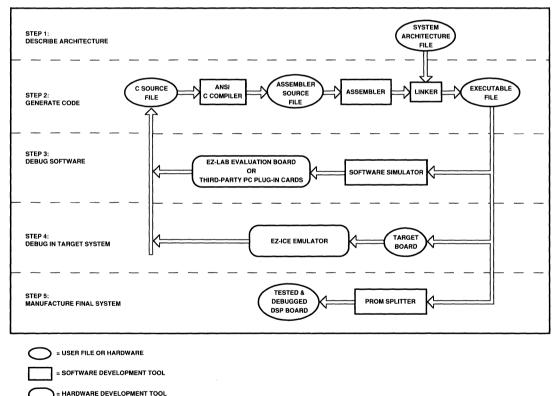

Figure 1.2 shows the process of developing an application using the development tools. File name extensions (.ASM, .OBJ, etc.) at the input and output of each step signify different types of files.

1-9

The development system includes the following:

**C Compiler & Runtime C Library**. The C Compiler reads source files written in ANSI-standard C language. The compiler outputs ADSP-21xxx assembly language files. It comes with a standard library of C-callable routines.

Numerical C Compiler. DSP/C<sup>™</sup> is Analog Devices' implementation of ANSI-standard Numerical C—a set of extensions to C that allow matrix data types and operators. The compiler outputs ADSP-21xxx assembly language files. With DSP/C, signal processing algorithms are easier to program and the compiled code is more efficient because the compiler directly translates matrix operations in Numerical C to the matrix capabilities of the ADSP-21020/21010.

**Assembler**. The assembler inputs a file of ADSP-21xxx source code and assembler directives and outputs a relocatable object file. The assembler supports standard C preprocessor directives as well as its own directives.

**Linker**. The linker processes separately assembled object and library files to create a single executable program. It assigns memory locations to code and data in accordance with a user-defined architecture file, a text file that describes the memory configuration of the target system.

**Assembly Library/Librarian**. The assembly library contains standard arithmetic and DSP routines that can be called from your program, saving development time. You can add your own routines to this library using the librarian function.

**Simulator**. The simulator executes an ADSP-21020/21010 program in software in the same way that the processor would in hardware. The simulator also simulates the memory and I/O devices specified in the architecture file. The simulator's window-based user interface lets you interactively observe and alter data contained in the processor's registers and in memory.

**PROM Splitter**. The PROM splitter translates an ADSP-21xxx executable program into one of several formats (Motorola S2 and S3, Intel Hex Record, etc.) that can be used to configure a PROM or be downloaded to a target from a microcontroller.